# **RTX-51**

Real-Time Multitasking Executive for the 8051 Microcontroller

User's Guide 03.02

ii Keil Software

Information in this document is subject to change without notice and does not represent a commitment on the part of the manufacturer. The software described in this document is furnished under license agreement or nondisclosure agreement and may be used or copied only in accordance with the terms of the agreement. It is against the law to copy the software on any medium except as specifically allowed in the license or nondisclosure agreement. The purchaser may make one copy of the software for backup purposes. No part of this manual may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or information storage and retrieval systems, for any purpose other than for the purchaser's personal use, without written permission.

© Copyright 1988-2002 Keil Elektronik GmbH., Mettler & Fuchs AG, and Keil Software, Inc.

All rights reserved.

Keil C51<sup>TM</sup> and μVision2<sup>TM</sup> are trademarks of Keil Elektronik GmbH. Microsoft<sup>®</sup> and Windows<sup>TM</sup> are trademarks or registered trademarks of Microsoft Corporation.

IBM®, PC®, and PS/2® are registered trademarks of International Business Machines Corporation.

Intel<sup>®</sup>, MCS<sup>®</sup> 51, ASM–51<sup>®</sup>, and PL/M–51<sup>®</sup> are registered trademarks of Intel Corporation.

Every effort was made to ensure accuracy in this manual and to give appropriate credit to persons, companies, and trademarks referenced herein.

08.03.2002

RTX-51 iii

# **Preface**

RTX-51 is a runtime library that, together with C51, allows real-time systems to be implemented for all processors of the 8051 family (e.g., 8051, 8052, 80515, etc.), except a few single chip processors with limited memory space, like the 8?C751 and 8?C752.

This user's manual assumes that the user is familiar with the programming of 8051 processors, experienced with the KEIL C51 high-level programming language, and has basic knowledge of real-time programming.

The following literature is recommended as an extensive introduction in the area of real-time programming:

- Deitel, H.M., Operating Systems, second edition, Addison-Wesley Publishing Company, 1990 (contains many additional literature references and is praxisorientated)

- Ripps, David, A Guide to Real-Time Programming, Englewood Cliffs, N.J, Prentice Hall, 1988.

- Allworth, S.T., Introduction to Real-Time Software Design, Springer-Verlag Inc., New York

- Richter, Lutz, Betriebssysteme,

Teubner Stuttgart, 1985 (theoretical view, german language)

- Goldsmith, Sylvia, A practical guide to Real-Time Systems Development, Prentice Hall

iv Preface

# **Manual Organization**

This user's guide is divided into eight chapters:

- "Chapter 1. Overview," provides a brief overview on RTX-51.

- "Chapter 2: Installation," describes the installation of RTX-51 and provides an overview on the necessary software tools.

- "Chapter 3: Programming Concepts," describes the ways RTX-51 functions can be used by your application and how the kernel handles C51 specific aspects.

- "Chapter 4: Programmer's Reference," contains a detailed listing of all RTX-51 system functions including examples.

- "Chapter 5: Configuration," describes the adaptation of RTX-51 to various members of the 8051 processor family and the system-configurable constants.

- "Chapter 6: CAN Support," introduces the driver software for a CAN bus interface using different controller hardware.

- "Chapter 7: BITBUS Support," introduces the driver software for a BITBUS interface using the intel 8044 on-chip controller.

- "Chapter 8: Application Example," describes as an example the software required to control the traffic lights at an intersection

vi Content

# **Contents**

| Chapter 1. Overview                                 | 1  |

|-----------------------------------------------------|----|

| Summary of the Major System Features                | 2  |

| Tasks                                               | 2  |

| Interrupt System                                    | 3  |

| System Clock                                        | 4  |

| Operating Resources                                 | 4  |

| Program Example                                     | 4  |

| Example Program for a Simplified RTX-51 Application | 5  |

| Compiling and Linking the Program                   |    |

| Extract from the MAP file generated by BL51         | 6  |

| Debugging the Program                               | 7  |

| Chapter 2. Installation                             | 9  |

| Software Requirements                               | 9  |

| Backing Up Your Disks                               |    |

| Installing the Software                             | 9  |

| Directory Structure                                 | 10 |

| Chapter 3. Programming Concepts                     | 11 |

| Task Management                                     |    |

| Task States                                         |    |

| Task Switching                                      | 12 |

| Task Classes                                        | 13 |

| Task Declaration                                    | 15 |

| Interrupt Management                                | 17 |

| Methods for Interrupt Handling                      | 17 |

| Handling of the 8051 Interrupt Enable Register      | 19 |

| Handling of the 8051 Interrupt Priority Register    | 20 |

| Declaration of C51 Interrupt Functions              | 20 |

| Task Communication                                  | 21 |

| Signals                                             | 21 |

| Wait for a Signal                                   | 21 |

| Send Signal                                         | 22 |

| Clear Signal                                        | 22 |

| Mailboxes                                           |    |

| Mailbox Lists                                       | 22 |

| Send a Message to a Mailbox                         | 23 |

| Read a Message from a Mailbox                       | 24 |

| Semaphores                                          | 24 |

| Wait for Token                                      | 25 |

| Send Token                                          | 25 |

| Dynamic Memory Management                           | 25 |

| Generate Memory Pool                                | 25 |

| Request Memory Block from Pool             | 26 |

|--------------------------------------------|----|

| Return Memory Block to Pool                |    |

| Time Management                            |    |

| Set Time Slice                             |    |

| Delay a Task                               |    |

| Cyclic Task Activation                     |    |

| Specific C51 Support                       |    |

| C51 Memory Models                          |    |

| Reentrant Functions                        |    |

| Floating-Point Operations                  |    |

| Use of the C51 Runtime Library             |    |

| Register Bank Default                      |    |

| Use of the C51 Special Library             |    |

| Code Bankswitching                         |    |

| -                                          |    |

| Chapter 4. Programmer's Reference          | 33 |

| Name Conventions                           |    |

| Return ValuesINCLUDE Files                 |    |

| Overview                                   |    |

|                                            |    |

| Initialize and Start the System            |    |

|                                            |    |

| os_start_system                            |    |

| Task Management Function Call Overview     |    |

|                                            |    |

| os_create_task                             |    |

| os_delete_task                             |    |

| os_running_task_id                         |    |

| Interrupt ManagementFunction Call Overview |    |

|                                            |    |

| os_attach_interrupt                        |    |

| os_detach_interrupt                        |    |

| os_enable_isr                              |    |

| os_disable_isr                             |    |

| oi_set_int_masks<br>oi_reset_int_masks     |    |

| Wait Function                              |    |

|                                            |    |

| Function Call Overviewos_wait              |    |

|                                            |    |

| Signal Functions                           |    |

|                                            |    |

| os_send_signal                             |    |

| os_clear_signalisr send signal             |    |

| 5                                          |    |

| Message Functions                          |    |

| COUNTRY ATT A VELVIEW                      |    |

| os_send_message                                                                                                                                                                                                                                 |                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|                                                                                                                                                                                                                                                 |                                               |

| isr_send_message                                                                                                                                                                                                                                | 72                                            |

| isr_recv_message                                                                                                                                                                                                                                |                                               |

| Semaphore Functions                                                                                                                                                                                                                             |                                               |

| Function Call Overview                                                                                                                                                                                                                          | 74                                            |

| os_send_token                                                                                                                                                                                                                                   | 75                                            |

| Memory Management                                                                                                                                                                                                                               |                                               |

| Function Call Overview                                                                                                                                                                                                                          |                                               |

| Example for a Buffer Pool Application                                                                                                                                                                                                           |                                               |

| os_create_pool                                                                                                                                                                                                                                  | 78                                            |

| os_get_block                                                                                                                                                                                                                                    | 80                                            |

| os_free_block                                                                                                                                                                                                                                   |                                               |

| Management of the System Clock                                                                                                                                                                                                                  |                                               |

| Function Call Overview                                                                                                                                                                                                                          |                                               |

| os_set_slice                                                                                                                                                                                                                                    | 85                                            |

| Debug Functions                                                                                                                                                                                                                                 | 86                                            |

| Function Call Overview                                                                                                                                                                                                                          | 86                                            |

| os_check_tasks                                                                                                                                                                                                                                  | 87                                            |

| os_check_task                                                                                                                                                                                                                                   | 89                                            |

| os_check_mailboxes                                                                                                                                                                                                                              | 91                                            |

| os_check_mailbox                                                                                                                                                                                                                                | 93                                            |

| os_check_semaphores                                                                                                                                                                                                                             | 95                                            |

| os_check_semaphore                                                                                                                                                                                                                              | 97                                            |

| os_check_pool                                                                                                                                                                                                                                   | 99                                            |

| Chapter 5. Configuration                                                                                                                                                                                                                        | 101                                           |

| User-Configuration  User-Configurable Values                                                                                                                                                                                                    |                                               |

| Memory Assignment                                                                                                                                                                                                                               |                                               |

| Direct-Addressable Internal Memory (DATA)                                                                                                                                                                                                       |                                               |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                           | 104                                           |

| Indinat Addressable Internal Manager (IDATA)                                                                                                                                                                                                    | 104                                           |

| Indirect-Addressable Internal Memory (IDATA)                                                                                                                                                                                                    |                                               |

| External Memory (XDATA)                                                                                                                                                                                                                         | 106                                           |

|                                                                                                                                                                                                                                                 | 106                                           |

| External Memory (XDATA)  Number of the Processor Type Used                                                                                                                                                                                      | 106                                           |

| External Memory (XDATA)                                                                                                                                                                                                                         | 106<br>108                                    |

| External Memory (XDATA)  Number of the Processor Type Used  Chapter 6. CAN Support  Introduction                                                                                                                                                | 106<br>108<br>117<br>117                      |

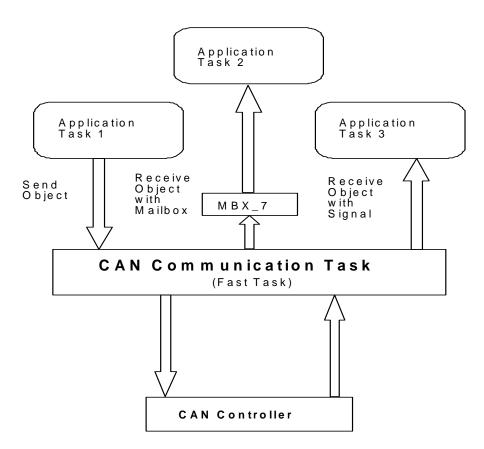

| External Memory (XDATA) Number of the Processor Type Used  Chapter 6. CAN Support  Introduction Concept                                                                                                                                         | 106<br>108<br>117<br>117                      |

| External Memory (XDATA) Number of the Processor Type Used  Chapter 6. CAN Support  Introduction Concept Application Interface                                                                                                                   | 106<br>108<br>117<br>117<br>118<br>120        |

| External Memory (XDATA) Number of the Processor Type Used  Chapter 6. CAN Support Introduction Concept Application Interface Function Call Overview                                                                                             | 106<br>108<br>117<br>117<br>118<br>120        |

| External Memory (XDATA) Number of the Processor Type Used  Chapter 6. CAN Support  Introduction  Concept  Application Interface  Function Call Overview  Function Call Description                                                              | 106<br>108<br>117<br>118<br>120<br>120<br>122 |

| External Memory (XDATA) Number of the Processor Type Used  Chapter 6. CAN Support  Introduction Concept Application Interface Function Call Overview Function Call Description can_task_create                                                  | 106108117118120120122123                      |

| External Memory (XDATA) Number of the Processor Type Used  Chapter 6. CAN Support  Introduction Concept  Application Interface  Function Call Overview  Function Call Description  can_task_create can_hw_init                                  | 106117117118120122123124                      |

| External Memory (XDATA) Number of the Processor Type Used  Chapter 6. CAN Support  Introduction Concept Application Interface Function Call Overview Function Call Description can_task_create can_hw_init can_def_obj                          | 106117117118120122123124129                   |

| External Memory (XDATA) Number of the Processor Type Used  Chapter 6. CAN Support Introduction Concept Application Interface Function Call Overview Function Call Description can_task_create can_hw_init can_def_obj can_def_obj_ext           | 106117117118120122123124129131                |

| External Memory (XDATA) Number of the Processor Type Used  Chapter 6. CAN Support Introduction Concept Application Interface Function Call Overview Function Call Description can_task_create can_hw_init can_def_obj can_def_obj_ext can_stop. | 106117117118120122123124129131                |

| External Memory (XDATA) Number of the Processor Type Used  Chapter 6. CAN Support Introduction Concept Application Interface Function Call Overview Function Call Description can_task_create can_hw_init can_def_obj can_def_obj_ext           | 106117117118120122123124129131133             |

| can_receive                                      | 139                                                     |

|--------------------------------------------------|---------------------------------------------------------|

| can_bind_obj                                     | 142                                                     |

| can_unbind_obj                                   | 144                                                     |

| can_wait                                         | 145                                                     |

| can_request                                      | 149                                                     |

| can_read                                         | 151                                                     |

| can_get_status                                   | 153                                                     |

| Configuration                                    | 154                                                     |

| Hardware Requirements                            | 154                                                     |

| Configuration Files                              | 154                                                     |

| Memory/System Requirements                       | 155                                                     |

| Adapting Stack Sizes                             |                                                         |

| Linking RTXCAN                                   | 156                                                     |

| Return Values                                    |                                                         |

| Timing / Initialization                          | 158                                                     |

| Quick Start                                      |                                                         |

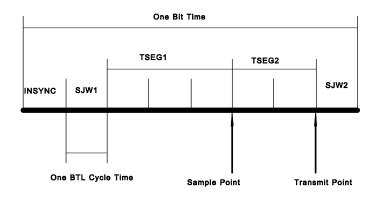

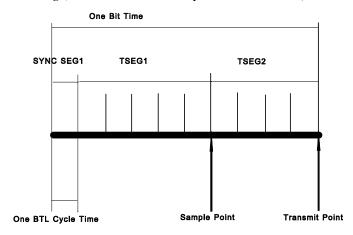

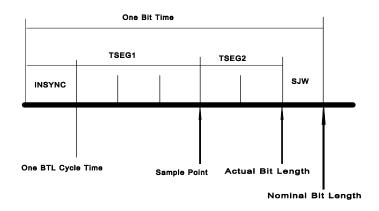

| Bit Timing                                       |                                                         |

| Sample Point Configuration Requirements          |                                                         |

| Intel 82526 Bus Timing                           |                                                         |

| Intel 82527 Bus Timing                           |                                                         |

| Infineon 81C90/91 Bus Timing                     |                                                         |

| Philips 82C200/80C592 Bus Timing                 |                                                         |

| Application Examples                             |                                                         |

| Files Delivered                                  | 100                                                     |

| Files Delivered                                  | 170                                                     |

|                                                  |                                                         |

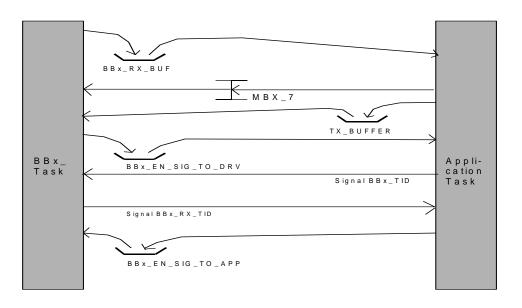

| Chapter 7. BITBUS Support (RTX-51)               | 201                                                     |

| Chapter 7. BITBUS Support (RTX-51) Introduction  | <b>201</b> 201                                          |

| Chapter 7. BITBUS Support (RTX-51)               | <b>201</b> 201202                                       |

| Chapter 7. BITBUS Support (RTX-51)               | <b>201</b> 201202202                                    |

| Chapter 7. BITBUS Support (RTX-51)               |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction | 201 202 202 206 206 207 207 210 210 211 212 214 215 216 |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| Chapter 7. BITBUS Support (RTX-51)  Introduction |                                                         |

| X | Content |

|---|---------|

|---|---------|

| ndex                           | 239 |

|--------------------------------|-----|

| Flossary                       | 236 |

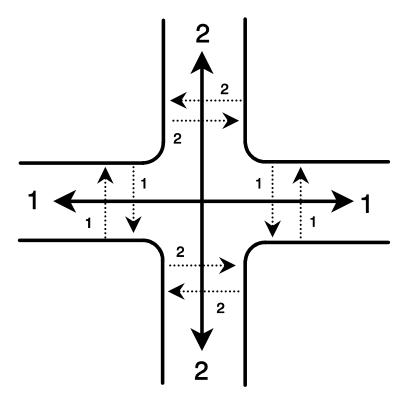

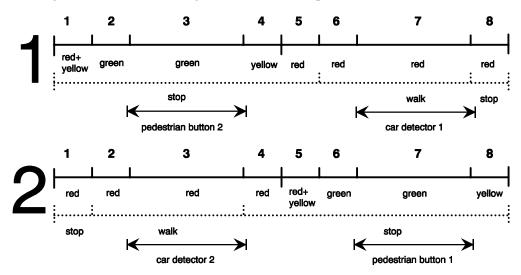

| Testing and Debugging TRAFFIC2 | 234 |

| Compiling and Linking TRAFFIC2 | 234 |

| GETLINE.C                      | 233 |

| SERIAL.C                       | 231 |

| TRAFFIC2.C                     | 223 |

| Software                       | 222 |

RTX-51 1

# Chapter 1. Overview

There are two fundamental problems of many modern microprocessor applications:

■ A task must be executed within a relatively short time frame.

Several tasks are time- and logic independent from one another and should therefore execute simultaneously on a

processor.

System ISR's

System Tasks

RTX Kernel

User Tasks

User ISR's

Figure 1: Overview processor family.

The first item is also referred to as a requirement for guaranteed response times, also designated as "real-time". The second item designates the typical situation of multi-program operation (multiprogramming, multi-tasking). In this case, the individual tasks are organized as independent computer processes (normally designated as a "task").

The RTX-51 Real-Time Multitasking Executive contains the functions to solve these types of problem definitions in a simple and effective way with all processors of the 8051

The sequence control required for simple applications could, of course, be implemented by the user himself. This, however, is not very efficient, since a large part of the functions which a multitasking executive already offers would have to be re-implemented.

Advantages in using a Real-Time Multitasking Executive:

- A program can be more easily implemented, tested and maintained by breaking down the problem to be solved into individual, easily comprehensible tasks.

- The modular approach allows individual tasks to be used in other projects.

- Since the real-time and multitasking problems which occur are already solved the time required for creating programs and testing is considerably reduced.

2 Overview

#### Advantages of RTX-51 are:

- Simple use of RTX-51 by integration in the Keil C51 development system.

- Complete support of all C51 features such as floating-point operations, reentrant functions and interrupt functions.

- User-friendly configuration of RTX-51 for all members of the 8051 family.

- Flexibility only requires a few system resources and can also be applied for time-critical applications.

# **Summary of the Major System Features**

### **Tasks**

RTX-51 recognizes two classes of tasks:

- Fast tasks with especially short responses and interrupt times. Each fast task uses an individual register bank of the 8051 and contains its own stack area. RTX-51 supports a maximum of three fast tasks active at a time.

- Standard tasks that require somewhat more time for the task switching, therefore less internal memory than the fast tasks. All standard tasks share a register bank and a stack area; during a task change the current contents of registers and the stack are stored in the external RAM. RTX-51 supports a maximum of 16 standard tasks active at a time.

RTX-51 tasks are declared as parameterless C functions with the attribute "\_task\_".

#### **Task Communication and Synchronisation**

RTX-51 provides two mechanisms so that the individual tasks can communicate with each other and synchronize tasks which normally execute independent of one another:

- Signals are the fastest form of task synchronisation. No actual information is exchanged only a stimulus is activated for a task.

- Messages are exchanged via so-called mailboxes. Mailboxes allow the buffered exchange of data. Tasks can be entered in queues for these in order

RTX-51 3

to wait for a message to be received. The individual messages are managed by the mailbox according to the FIFO principle (First-In, First-Out). If several tasks are waiting for a message to be received, the task which is waiting the longest (first in the queue) receives the message.

■ Semaphores are simple protocol mechanisms that share common resources without access conflicts. By use of token's resources may be managed in such a way that only one task at a time is allowed to use them. If more than one task requests access to a resource, then the first task will be granted access, while the second task is put on a waiting list until the first task finishes its operations on this resource.

#### **Task Switching**

RTX-51 contains an event-driven task switching mechanism that switches tasks according to their priority (preemptive multitasking). An additional task switching mechanism which switches according to the time-slice mode can be optionally used (round-robin scheduling).

RTX-51 recognizes four priority levels; priorities 0, 1 and 2 can be assigned to standard tasks. Priority 3 is reserved for fast tasks.

The individual tasks can wait for various events to occur without requiring processor time (no processor burdening). Events can be characterized as the receipt of messages, signals, interrupts and time-outs, or a combination of these.

Three wait forms are supported:

- Normal: the WAITING (BLOCKED) task can be blocked for an arbitrary amount of time until the corresponding event occurs.

- Conditional: the waiting task is never blocked, the task can recognize if the corresponding event existed by evaluating the return value.

- With time-out: the task is blocked for a certain time if the corresponding event does not occur.

### **Interrupt System**

RTX-51 performs task synchronisation for external events by means of the interrupt system. Two types of interrupt processing are basically supported in this case:

4 Overview

1

1. C51 Interrupt Functions

Interrupts are processed by C51 interrupt functions.

2. Task Interrupts

Interrupts are processed by fast or standard tasks of RTX-51.

The methods of interrupt processing can be selected depending on the application. The individual methods can also be combined in an application.

### **System Clock**

The RTX-51 system clock is based on hardware Timer 0, 1 or 2 (can be configured) of the 8051 processor. It supplies the basic pulse (clock frequency) required for the time-outs and for the round-robin scheduling.

### **Operating Resources**

RTX-51 requires the following 8051 system resources:

■ CODE Memory:

Approx. 6 to 8 Kbytes, depending on the function scope used.

■ Internal (DATA and IDATA) RAM:

40 to 46 bytes for system data (depending on the selected processor type). 20 to 200 bytes for the stack (can be configured by the user). Register bank 0 for standard tasks; register banks 1, 2 and 3 for fast tasks or C51 interrupt functions.

- External (XDATA) RAM: Minimal 450 bytes.

- Timer 0, 1 or 2 for the system clock (can be configured by the user).

### **Program Example**

The following simplified example illustrates the basic design of a RTX-51 application and the procedure for compiling and linking:

RTX-51 5

# Example Program for a Simplified RTX-51 Application

```

#pragma large

// RTX-51 Definitions

#include <Rtx51.h>

#define PRODUCER_NBR

// Tasknumber for the producer task

#define CONSUMER_NBR

1

// Tasknumber for the consumer task

#define FIRST_MAILBOX

0

// The mailbox identification

#define WAIT_FOREVER

0xFF

// A constant, signalling to the RTX

// call, that no timeout for the call is

// expected.

void ProducerTask (void) _task_ PRODUCER_NBR

unsigned int MessageToSend = 1;

os_create_task (CONSUMER_NBR);

// Create the Consumer-Task

for (;;)

// endless loop

// Send the actual value of 'send_mes' to mailbox 0

// if the mailbox is full, wait until there is place for the message

os_send_message (FIRST_MAILBOX, MessageToSend, WAIT_FOREVER);

MessageToSend++;

void ConsumerTask (void) _task_ CONSUMER_NBR _priority_ 1

unsigned int ReceiveBuffer;

for (;;)

// Read from mailbox FIRST_MAILBOX one message

// Wait for a message, if the mailbox is empty

os_wait (K_MBX + FIRST_MAILBOX, WAIT_FOREVER, &ReceiveBuffer);

// ... perform some calculations with the message

}

void main (void)

signed char RtxReturnState;

// Init the system and start the Producer-Task

RtxReturnState = os_start_system (PRODUCER_NBR);

```

6 Overview

1

### **Compiling and Linking the Program**

The most convenient way is to use  $\mu$ Vision2 for this purpose. A project definition file named SAMPLE.UV2 identifies all required files, all required settings are derived from the file SAMPLE.OPT. Use 'Open project' from the 'Project' menu to select the project file. SAMPLE.UV2 can be found in the C51\RTX51\Examples\Sample folder.

By use of the 'Build target' selection out of the 'Project' menu the sample program is compiled and linked in one step.

### Extract from the MAP file generated by BL51

BL51 generates a task list which lists all tasks defined in the system along with their identification number, the defined priority and the register bank used

```

BL51 BANKED LINKER/LOCATER V4.20, INVOKED BY:

C:\KEIL\C51\BIN\BL51.EXE Sample.obj, Rtxconf.obj TO Sample RTX51

MEMORY MODEL: LARGE

INPUT MODULES INCLUDED:

Sample.obj (SAMPLE)

Rtxconf.obj (?RTX?CONFIGURATION)

C:\KEIL\C51\LIB\RTX51.LIB (RTXCLK)

C:\KEIL\C51\LIB\RTX51.LIB (RTXCREA)

C:\KEIL\C51\LIB\RTX51.LIB (RTXDATA)

C:\KEIL\C51\LIB\RTX51.LIB (RTXINIT)

C:\KEIL\C51\LIB\RTX51.LIB (RTXINT)

C:\KEIL\C51\LIB\RTX51.LIB (RTXSEND)

C:\KEIL\C51\LIB\RTX51.LIB (RTXWAIT)

C:\KEIL\C51\LIB\RTX51.LIB (RTX51 LIB

VERSION 0V700)

C:\KEIL\C51\LIB\RTX51.LIB (RTX2C51)

C:\KEIL\C51\LIB\RTX51.LIB (RTXBLOCK)

C:\KEIL\C51\LIB\RTX51.LIB (RTXDISP)

C:\KEIL\C51\LIB\RTX51.LIB (RTXIHAND)

C:\KEIL\C51\LIB\RTX51.LIB (RTXINS)

C:\KEIL\C51\LIB\RTX51.LIB (RTXQUOP)

C:\KEIL\C51\LIB\C51L.LIB (?C_STARTUP)

TASK TABLE OF MODULE: Sample (SAMPLE)

TASKID PRIORITY REG-BANK SEGMENT NAME

?PR?PRODUCERTASK?SAMPLE

?PR?CONSUMERTASK?SAMPLE

```

RTX-51 7

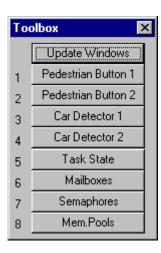

### **Debugging the Program**

The  $\mu Vision2$  debugger is started automatically upon completion of the link step. A predefined debugger initialization file (SIMULATOR.INI) is processed. The application code and an include file named DBG\_RTX.INC are loaded. This file contains declarations of  $\mu Vision2$  debugger functions to support debugging of RTX-51 code. The functions may be called by pressing buttons in the toolbox window:

■ With the button 'Task State' a table of all declared tasks may be displayed. It shows some important information about them and the associated task states.

| ID                         | Start                                              | Prio                       | State                                                         | Blocked for Event        | Mbx/Sem     | Timer | Signal |

|----------------------------|----------------------------------------------------|----------------------------|---------------------------------------------------------------|--------------------------|-------------|-------|--------|

| 0<br>4<br>5<br>1<br>2<br>3 | 0032H<br>014AH<br>0164H<br>00A7H<br>00FDH<br>0117H | 0<br>1<br>0<br>1<br>3<br>3 | RUNNI NG<br>BLOCKED<br>READY<br>BLOCKED<br>BLOCKED<br>BLOCKED | TKN<br>MSG<br>TKN<br>TMO | 9<br>Ø<br>9 | 7     | 88888  |

ID Task number, as defined in the task-declaration.

Start Task start address.

Prio Task priority.

State Actual task state.

Blocked for Event Defines for which event the task is blocked

(the task is waiting for). Event codes used here are:

MSG: wait for message (mailbox read)

INT: wait for interrupt SIG: wait for signal TMO: wait for time-out

WRITE-

MAILBOX: wait until enough space in message

list of mailbox (mailbox write)

TKN: wait for a token (from a semaphore)

Mbx/Sem: When the task is blocked for a

mailbox read/write, then this field shows the mailbox number [0..7]. When the task is blocked for a semaphore, then this field shows the

semaphore number [8..15].

Timer: When the task is blocked for a time-

8 Overview

out, then this field shows the

remaining number of system ticks to

time-out

Signal: State of task signal flag (1=set,

0=reset

■ With the button 'Mailboxes' a list of all pre-defined mailboxes may be displayed.

| Mbx                                  | Msg      | Read     | Write    | Messages                   |

|--------------------------------------|----------|----------|----------|----------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 93199999 | 19999999 | 00000000 | 0001H/1200H/34FFH<br>5800H |

Mbx Mailbox number [0..7].

Msg Number of messages in this mailbox.

Read Number of tasks which are blocked for reading a

message.

Write Number of task which are blocked for writing a

message.

Messages Shows the messages contained in the mailbox.

■ With the button 'Semaphores' a list of all pre-defined semaphores may be displayed.

| Sem                                        | Tkn      | Wait                            |

|--------------------------------------------|----------|---------------------------------|

| 8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | 00010001 | 0<br>3<br>1<br>0<br>1<br>0<br>0 |

Sem Semaphore number [8..15].

Tkn State of token flag (1=token available; 0=else). Wait Number of tasks which are blocked for a token.

RTX-51 / RTX-251 9

# Chapter 2. Installation

This chapter explains how to setup an operating environment and how to install the software on your hard disk. Before starting the installation program, you must do the following:

- Verify that your computer system meets the minimum requirements.

- Make a copy of the installation diskette for backup purposes.

# **Software Requirements**

The following products are required to use RTX-51 together with Keil C51:

- C51 Compiler Version 5.02 or later

- BL51 Linker for Code-Banking Version 3.52 or later

- A51 Assembler Version 5.02 or later

- RTX-51 Real-Time Executive Version 7.00 or later

# **Backing Up Your Disks**

We strongly suggest that you make a backup copy of the installation diskettes. Then, use the backup disks to install the software. Be sure to store the original disks in a safe place in case your backups are lost or damaged.

# **Installing the Software**

RTX-51 come with an installation program which allows easy installation under MS-WINDOWS.

The following versions are supported:

- MS-WINDOWS 95 or later

- MS-WINDOWS NT Version 3.5 or later

To install RTX-51 ...

10 Installation

2

- Insert the first product diskette into Drive A,

- Run A:\SETUP.EXE,

- Follow the instructions displayed by the installation program

#### NOTE:

■ The PK51 product must be installed before installing RTX-51.

# **Directory Structure**

The installation program copies the RTX-51 files into sub-directories of the PK51 base directories.

After creating the appropriate directory (if required), the installation program copies the files into the sub-directories listed in the following table.

| Subdirectory         | Description                                      |

|----------------------|--------------------------------------------------|

| \C51\RTX51\Kernel    | All source files of RTX-51                       |

| \C51\RTX51\Examples\ | RTX-51 configuration files, sample applications. |

| \C51\RTX51\CAN\      | CAN support                                      |

| \C51\RTX51\BITBUS    | BITBUS support                                   |

| \C51\LIB             | Library files.                                   |

This table shows a complete installation. Your installation may vary depending on the products you installed.

RTX-51 / RTX-251 11

# **Chapter 3. Programming Concepts**

# Task Management

The main function of tasks within a Real-Time Multitasking Executive is the time-critical processing of external or internal events. A priority can be assigned to the individual tasks to differentiate between which are most important. In this case, value 3 corresponds to the highest priority and value 0 corresponds to the lowest priority.

RTX-51 always assigns the READY task with the highest priority to the processor. This task only maintains control over the processor until another task with a higher priority is ready for execution, or until the task itself surrenders the processor again (preemptive multitasking).

If several READY tasks exist with the priority 0, a task switching can optionally occur after completion of a time slice (round-robin scheduling).

Use the following guideline when assigning task priorities:

The application should work error free regardless task priorities. The priorities only serve for time optimizing.

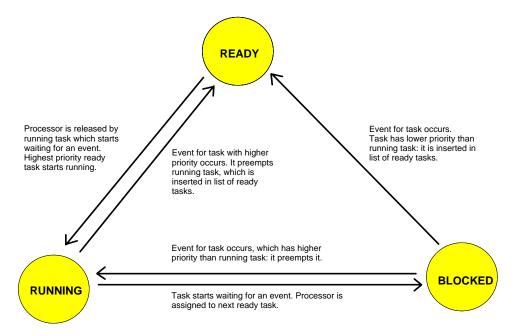

### **Task States**

RTX-51 recognizes four task states:

READY All tasks which can run are READY. One

of these tasks is the RUNNING (ACTIVE)

task.

RUNNING (ACTIVE) Task which is currently being executed by

the processor. Only one task (maximum)

can be in this state at a time.

BLOCKED (WAITING) Task waits for an event.

SLEEPING All tasks which were not started or which

have terminated themselves are in this state.

An event may be the reaching of a period of time, the sending of a message or signal, or the occurrence of an interrupt. These types of events can lead to state changes of the tasks involved; this, on the other hand, can produce a task switching (task change, task switch).

The states "READY", "RUNNING" and "BLOCKED" are called active task states, since they can only be accepted by tasks which were started by the user (see system function "os\_create\_task"). "SLEEPING" is an inactive task state. It is accepted from all tasks which were declared but still have not been started.

Figure 2: Task States

The figure shows the three active task states and their interaction.

### **Task Switching**

The RTX-51 system section which the processors assigns to the individual tasks is referred to as the scheduler (also dispatcher).

The RTX-51 scheduler works according to the following rules:

■ The task with the highest priority of all tasks in the READY state is executed.

- If several tasks of the same priority are in the READY state, the task thay has been ready the longest will be the next to execute.

- Task switchings are only executed if the first rule would have been otherwise violated (exception: round-robin scheduling).

These rules are strictly adhered to and never violated at any time. As soon as a task yields a state change, RTX-51 checks whether a task change is necessary based on the scheduling rules. Time-slice task change (round-robin scheduling) are executed if the following conditions are satisfied:

- Round-robin scheduling must be enabled (see configuration).

- The RUNNING task has the priority of 0 and is currently not executing a floating-point operation (see section "Floating-Point Operations", page 28).

- At least one task with the priority zero must be in the READY state.

- The last task change must have occurred after the selected system time interval (see system function "os\_set\_slice"). The system time interval can be changed dynamically during program execution.

The operating mode preferred by RTX-51 is the preemptive scheduling. If desired by the user, the tasks with the priority zero can additionally be managed by means of the round-robin scheduling.

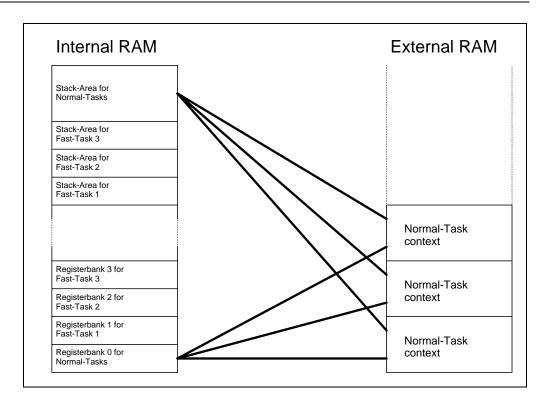

### **Task Classes**

RTX-51 basically recognizes two classes of tasks:

#### **Fast Tasks**

- Contain especially short responses and interrupt disable times.

- Contain a separate register bank and a separate stack area (register banks 1, 2 and 3).

- Contain the highest task priority (priority 3) and can therefore interrupt standard tasks.

- All contain the same priority and can therefore not be mutually interrupted.

- Can be interrupted by C51 interrupt functions.

- A maximum of three fast tasks can be active in the system.

Figure 3: Task Classes and Memory Allocation

#### **Standard Tasks**

- Require somewhat more time for the task switching compared to fast tasks.

- Share a common register bank and a common stack area (register bank 0).

- The current contents of registers and stack are stored in the external (XDATA) memory during a task change.

- Can be interrupted by fast tasks.

- Can interrupt themselves mutually.

- Can be interrupt by C51 interrupt functions.

- A maximum 16 standard tasks can be active in the system.

Each standard task contains a context area in the external memory. During a task change with standard tasks, all required registers of the running task and of the standard task stack are stored in the corresponding context area. Afterwards, the

registers and the standard task stack are reloaded from the context area of the task to be started (swapping).

In the case of fast tasks, a task change occurs considerably faster than for standard tasks, since each fast task has a separate register bank and a separate stack area. During a task change to a fast task, only the active register bank and the current stack pointer value must be changed.

### **Task Declaration**

C51 provides an extended function declaration for defining tasks.

A task is declared as follows:

#### void func (void) [model] \_task\_ <taskno> [\_priority\_ <prio>]

- Tasks cannot return a value (return type "void").

- No parameter values can be passed to tasks ("void" in parameter list).

- <taskno> is a number assigned by the user in the range 0...255. Each task must be assigned a unique number. This task number is required in RTX-51 system function calls for identifying a task. A maximum of 256 tasks can be defined. However, only 19 tasks can be active at the same time.

Note: If the XDATA memory requirement of RTX-51 is to be minimized, the tasks must be numbered sequentially beginning with the number 0.

- Standard tasks: Priorities 0, 1 and 2

- Fast tasks: Priority 3

If no priority is specified, RTX-51 uses the task priority 0.

■ Standard tasks must be compiled for register bank 0 which is the default value of the C51 compiler. Fast tasks must be compiled for register banks 1, 2 or 3. This must be guaranteed using the directive "#pragma REGISTERBANK (x)" (where x = 1, 2, 3). If this rule is violated, C51/BL51 generates an error message.

**Example 1:** Standard task with task number 8 and priority 0

```

void example_1 (void) _task_ 8 _priority_ 0

Of

void example_1 (void) _task_ 8

```

**Example 2:** Fast task with task number 134 and register bank 1

```

#pragma REGISTERBANK (1)

void example_2 (void) _task_ 134 _priority_ 3

```

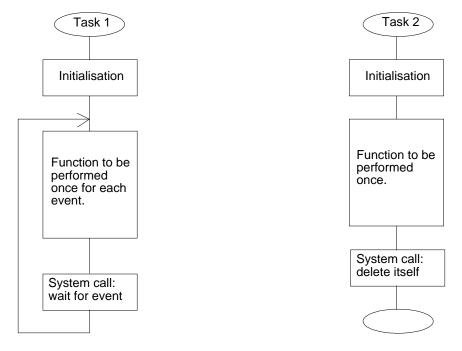

■ Example of typical task layouts:

Figure 4: Typical Task Layouts

Task 1 shown in the figure above has to perform a certain action each time an event occurs. Such an event may be a received message, a signal or a time-out, just to mention a few.

After completing its action it will start to wait for a new event. In this way the task will not consume time just waiting for the next event.

RTX-51 / RTX-251 17

Task 2 shown in the figure above has to perform just one specific action. It will delete itself after completing its job. Such a task may be, for example, a self test, which has to be executed once at power-up. It is often desirable to write such a self test routine as a separate task, than packing it in a routine.

# **Interrupt Management**

The management and processing of hardware interrupts is one of the major jobs of a Real-Time Multitasking Executive. RTX-51 provides various types of interrupt handling. The usage depends on the application requirements.

### **Methods for Interrupt Handling**

RTX-51 provides two different methods for handling interrupts. One of the two methods can be additionally divided into two sub-classes:

- (1) C51 Interrupt functions

- (2) RTX-51 task interrupts: Fast task interrupts Standard task interrupts

Method (1) corresponds to the standard C51 interrupt functions which can even be used without RTX-51 (also referred to as ISR, Interrupt Service Routine). When an interrupt occurs, a jump is made to the corresponding interrupt function directly and independent of the currently running task. The interrupt is processed outside of RTX-51 and therefore independent of the task scheduling rules.

With method (2), a fast or standard task is used to handle an interrupt. As soon as this interrupt occurs, the WAITING (BLOCKED) task is made READY and started according to the task scheduling rules. This type of interrupt processing is completely integrated in RTX-51. A hardware interrupt is handled identical to the receipt of a message or a signal (normal event within RTX-51).

The possible methods to handle interrupts have specific advantages and disadvantages, as described in greater detail in the following section. One of the methods can be selected depending on the requirements of the interrupt source

and the application. The methods can be combined in any form within a program.

The following summary illustrates the special features of the individual methods for handling interrupts:

| Method                         | C51 Interrupt<br>Function (ISR)                    | Fast Task                                                      | Standard Task                                                     |

|--------------------------------|----------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------|

| Interrupt Response<br>Time     | very fast                                          | fast                                                           | slow                                                              |

| Interrupts Disabled<br>During  | very short,<br>system functions                    | critical system<br>functions,<br>other fast tasks              | all system functions, fast tasks                                  |

| Interruptable With             | -                                                  | ISR                                                            | ISR,<br>fast tasks,<br>standard tasks with<br>higher priority     |

| System Resources<br>Used       | many<br>(stack and usually<br>extra register bank) | many<br>(stack and extra<br>register bank)                     | few (stack and register bank is shared with other standard tasks) |

| Interrupt Assignment           | static<br>(only one interrupt<br>source per ISR)   | dynamic<br>(multiple interrupt<br>sources per task<br>allowed) | dynamic<br>(multiple interrupt<br>sources per task<br>allowed)    |

| Allowed RTX-51<br>System Calls | some special                                       | all                                                            | all                                                               |

There are considerable differences in timing between the different methods. Please refer to timing specifications for more details.

The following points of emphasis deal with the features of the individual methods for handling interrupts mentioned above:

#### **■** C51 Interrupt Functions

Very sudden, periodically occurring interrupts without large coupling with the rest of the system (only infrequent communication with RTX-51 tasks, etc.).

Very important interrupts which must be served immediately independent of the current system state.

#### **■** Fast Task Interrupts

Important or periodic interrupts which must heavily communicate with the rest of the system when they occur.

#### ■ Standard Task Interrupts

RTX-51 / RTX-251 19

Only seldom occurring interrupts which must not be served immediately.

RTX-51 shows considerable different response times for fast and standard tasks.

### Handling of the 8051 Interrupt Enable Register

RTX-51 must have sole control over the Interrupt Enable register of the 8051 in order to adhere to the dispatcher rules and guarantee error-free execution of interrupt functions.

# The INTERRUPT ENABLE registers of the 8051 are managed by RTX-51 and must not be directly manipulated by the user!

RTX-51 controls the INTERRUPT ENABLE bits of the 8051 according to the following rules:

- ISR interrupts can interrupt all tasks and system functions at any time. The ISR interrupts are disabled only during a few very short system code sequences.

- The ISR interrupts can be disabled and enabled at the user's option using two system functions (see "os\_enable\_isr" and "os\_disable\_isr").

- Interrupt sources assigned to a task are only enabled if the task is actually waiting for an interrupt to occur. This prevents unexpected interrupts from occurring in the system.

- If the running task is a fast task, all task interrupts are disabled (not ISR interrupts, however). A relatively unimportant interrupt therefore cannot interrupt the fast tasks.

- If the running task is a standard task, it can be interrupted by all interrupts which occur. If another standard task is waiting for one of these occurring interrupts, it is made READY by RTX-51. However, it is only allocated to the processor if it contains a higher priority than the currently running task (standard scheduling).

- All standard task interrupts are disabled during the execution of system functions.

- The system clock interrupt (hardware Timer 0 or 1) is handled the same as for a fast task interrupt.

### Handling of the 8051 Interrupt Priority Register

The Interrupt Priority registers of the 8051 (not to be confused with the software task priorities) are not influenced by RTX-51. Even in normal operation (all interrupts at the same hardware priority), RTX-51 ensures that ISR interrupts are handled with preference. If desired, however, the ISR interrupts of the application can be set to a higher interrupt priority. RTX-51 does not provide any operations for the management of the Interrupt Priority registers.

All RTX-51 task interrupts must run at the same hardware interrupt priority! ISR interrupts may also run on an optional hardware interrupt priority. An optimal ISR processing is not guaranteed, however, if task and ISR interrupts are set to the same hardware priority.

### **Declaration of C51 Interrupt Functions**

Interrupt functions are declared as follows (see also C51 documentation):

void func (void) [model] [reentrant] interrupt n [using n]

- When interrupt functions are used, a difference must be made whether register bank switching (using-attribute) is used or not.

- With Register Bank Switching:

When entered, the interrupt function saves the registers ACC, B, DPH, DPL and PSW to the stack of the interrupted task, when necessary. Since not all registers are stored, the user must ensure that the interrupt function does not use a register bank used by RTX-51. Register bank 0 must also not be used (reason: it is always used by standard tasks and by the system clock). Register banks 1, 2 or 3 may only be used if they are not simultaneously being used by fast tasks.

■ Without Register Bank Switching:

If no using-attribute is used, all registers required are saved on the stack. This produces longer run times and increased stack requirement; for this purpose, register banks used by RTX-51 may also be used.

■ C51 interrupt functions with using-attribute must never use register bank 0 or one of the register banks used by a fast task.

RTX-51 / RTX-251 21

### **Task Communication**

The individual tasks within a real-time system can be dependent upon each other in various ways. These can use common data, exchange information with each other, or coordinate the activities for solving tasks.

RTX-51 provides the mailbox and signal concept for handling these types of task-related jobs.

### **Signals**

Signals represent the simplest and fastest form of task communication. These can always be used when a pure task synchronisation is required without data exchange.

Each active task contains its own signal flag with which the following operations can be executed:

- Wait for a signal

- Send signal

- Clear signal

The task number (see section section "Task Declaration", page 15) of the receiver task is used for identifying the signals for the individual operations.

### Wait for a Signal

Each task can wait for its signal flag (system function "os\_wait"). It waits until its signal flag is set by another task (system function "os\_send\_signal"). After a signal is received, the waiting task clears its signal flag again and enters the task state READY or RUNNING, depending on priority relationships.

If the signal flag is already set when the task calls the wait function (when the signal flag was previously set by another task), then it immediately receives the signal. The task does not first enter the WAIT state (BLOCKED).

The waiting time for a signal can be restricted. If the specified time has expired without receiving the signal, the waiting task is made READY again with the return status "time-out" (see system function "os\_wait", page 59).

### **Send Signal**

Each task and each interrupt function can set the signal flag of any other task (send a signal to this task). Only one signal which has been sent can be stored per task (signal flag). As long as a task has not received a signal, each additional signal sent is lost.

### Clear Signal

A task can clear the signal flag of any other task (even its own). This allows defined signal states in the system at any time.

### **Mailboxes**

By means of the mailbox concept, messages can be exchanged free of conflicts between the individual tasks.

RTX-51 provides a fixed number of eight mailboxes. Messages can be exchanged in words (2 bytes) via these mailboxes. In this case, a message can represent the actual data to be transferred or the identification of a data buffer (defined by the user). In comparison to the signals, mailboxes are not assigned a fixed task, but can be freely used by all tasks and interrupt functions. These are identified with a mailbox number.

Mailboxes allow the following operations:

- Send a message

- Read a message

#### **Mailbox Lists**

Each mailbox internally consists of three wait lists. The user does not have direct access to these lists. Knowledge of their functions is, however, an advantage for understanding mailbox functions.

Wait lists can comprise the following states in operation:

| State Description                                    | Message List | Write Wait List | Read Wait List |

|------------------------------------------------------|--------------|-----------------|----------------|

| No messages,<br>no wait tasks                        | empty        | empty           | empty          |

| No messages, tasks exist that want to read           | empty        | empty           | not empty      |

| Messages exist,<br>no wait tasks                     | not empty    | empty           | empty          |

| Message list is full, tasks exist that want to write | full         | not empty       | empty          |

The three lists do have the following functions:

- (1) Message list List of the messages written in the mailbox. These comprise a maximum of eight messages.

- (2) Write wait list Wait list for tasks which want to write a message in the message list of the mailbox (maximum 16 tasks).

- (3) Read wait list Wait list for tasks which want to read a message from the message list of the mailbox (maximum 16 tasks).

All three lists are implemented as a FIFO queue (First-In, First-Out) without priority assignment; i.e., when read, the task which waits the longest (first in the queue) becomes the oldest messages in the mailbox.

### Send a Message to a Mailbox

Each task can send a message to any arbitrary mailbox. In this case, the message to be sent is copied in the message list. The sending task therefore has free access to the message after the sending.

If the message list of the mailbox is already full during the sending, the task is placed in the wait state (entered in the write wait list). It remains in the wait state until another task fetches a message from the mailbox and, thus, provides space. As an alternative, a time limit can also be specified for the sending after the waiting is aborted (if the message could not be entered in the mailbox).

If the message list is not full when the sending occurs, the message is immediately copied in the message list and the task must not wait.

### Read a Message from a Mailbox

Each task can read a message from an arbitrary mailbox. If the message list of the mailbox is currently empty (no

message available), the task is placed in the wait state (entered in the read wait list).

It remains in the wait state until another task sends a message to the mailbox. As an alternative, a time limit can also be specified for the reading after which the waiting is to be aborted (if no message is available).

If the message is not empty when reading, then the reading task immediately receives the message. It must not wait in this case.

### **Semaphores**

By means of the semaphore concept, resources can be shared free of conflicts between the individual tasks.

In a multi-tasking system there is often competition for resources. When several tasks can use the same portion of memory, the same serial I/O channel or another system resource, you have to find a way to keep the tasks out of each other's way. The semaphore is a protocol mechanism, which is used primarily to control access to shared resources (mutual exclusion).

A semaphore contains a token that your code acquires to continue execution. If the resource is already in use, the requesting task is blocked until the token is returned to the semaphore by its current owner.

There are two types of semaphores: binary semaphores and counting semaphores. As its name implies, a binary semaphore can only take two values: zero or one (token is in or out). A counting semaphore, however, allows values between zero and 65535.

RTX-51 provides a fixed number of eight semaphores of the binary type.

Semaphores allow the following operations:

- Wait for token

- Return (send) token

RTX-51 / RTX-251 25

#### Wait for Token

A task requesting a resource controlled by a semaphore can obtain a token from this semaphore by a wait operation (see system function "os\_wait"). If a token is available the task will continue its execution. Otherwise it will be blocked until the token is available or an optional time limit is exceeded.

#### Send Token

After completing its operation on a resource a task will return the associated token to the semaphore by a send function (see system function "os\_send\_token").

# **Dynamic Memory Management**

Dynamic memory space is often desired in a multitasking system for generating intermediate results or messages. The requesting and returning of individual memory blocks should be possible within constant time limits in a real-time system.

Memory management, which functions with memory blocks of variable size such as the standard C functions "malloc()" and "free()," is less suitable for this reason.

RTX-51 uses a simple and effective algorithm, which functions with memory blocks of a fixed size. All memory blocks of the same size are managed in a so-called memory pool. A maximum of 16 memory pools each a different block size can be defined. A maximum of 255 memory blocks can be managed in each pool.

### **Generate Memory Pool**

The application can generate a maximum of 16 memory pools with various block sizes. The application must provide an XDATA area for this purpose. The pool is stored and managed by RTX-51 in this area (see system function "os\_create\_pool").

### **Request Memory Block from Pool**

As soon as a pool has been generated, the application can request memory blocks. The individual pools are identified by their block size in this case.

If an additional block is still free in the pool, RTX-51 supplies the start address of this block to the application. If no block is free, a null pointer is returned (see system function "os\_get\_block").

### **Return Memory Block to Pool**

If the application no longer needs a requested memory block, it can be returned to the pool for additional use (see system function "os\_free\_block").

# **Time Management**

RTX-51 maintains an internal time counter, which measures the relative time passed since system start. The physical source of this time base is a hardware timer that generates an interrupt periodically. The time passed between these interrupts is called a system time slice or a system tick.

This time base is used to support time dependent services, such as pause or timeout on a task wait.

Three time-related functions are supported:

- Set system time slice

- Delay a task

- Cyclic task activation

### **Set Time Slice**

The period between the interrupts of the system timer sets the "granularity" of the time base. The length of this period, also called a time slice, can be set by the application in a wide range (see system function "os\_set\_slice").

### **Delay a Task**

A task may be delayed for a selectable number of time slices. Upon calling this system function the task will be blocked (sleep) until the specified number of system ticks has passed (see system function "os\_wait").

### **Cyclic Task Activation**

For many real-time applications it is a requirement to do something on a regular basis. A periodic task activation can be achieved by the RTX interval wait function (see system function "os\_wait"). The amount of time spent between two execution periods of the same task is controlled, using os\_wait, and is measured in number of system ticks and may be set by the application.

## **Specific C51 Support**

Apart from the use of C51 interrupt functions for fast processing of hardware interrupts, RTX-51 also supports the most extensions of the C51 compiler.

The following sections provide an overview on the use of C51 specific features together with RTX-51.

### **C51 Memory Models**

A RTX-51 application can use all memory models supported by C51 (SMALL, COMPACT, LARGE). However, the COMPACT model is normally reserved for reentrant functions (see section "Reentrant Functions" below).

The selected memory model influences only the location of the application objects. A part of the RTX-51 system variables is always stored in external (XDATA) memory. All RTX-51 applications require external memory. Applications without external memory are not possible.

Typical RTX-51 applications are normally implemented in the LARGE model. Variables whose access is time critical can optionally be located in internal RAM.

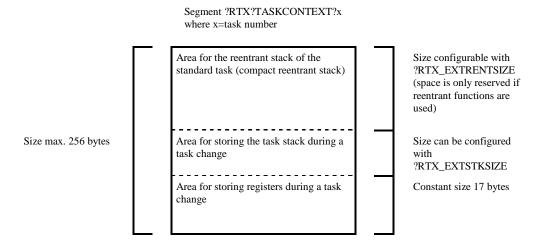

### **Reentrant Functions**

Normal C51 functions must not be simultaneously used by several tasks or interrupt functions. These functions store their parameters and local data in static memory segments. For this reason, this data is overwritten in the case of multiple calls.

In order to solve this problem, C51 provides reentrant functions (see C51 documentation). In the case of reentrant functions, the parameters and local data are protected against multiple calls, since a separate stack is created for them. RTX-51 supports the use of reentrant functions in the COMPACT model. In this case, a separate reentrant stack whose size can be configured is managed for each task. Interrupt functions use the reentrant stack of the interrupted RTX-51 task.

- RTX-51 only supports reentrant functions in the COMPACT model.

- Each task contains a separate reentrant stack configurable in size.

- Reentrant functions may be used in combination with non-reentrant functions of the SMALL and LARGE models. Simultaneous use of reentrant functions and non-reentrant functions is not allowed in the COMPACT model!

### **Floating-Point Operations**

The following section is intended for users of C51 versions older than V5.0. No special restrictions apply for other C51 users!

In principle, RTX-51 tasks can execute all types of operations with floating-point numbers. Since the C51 floating-point library is not implemented as reentrant (DK/PK51 versions older than V5.0), a running operation must not be interrupted by another operation. In order to guarantee this, certain precautionary measures must be assured.

No restrictions apply in the use of floating-point operations in the following two cases:

Only one task (with optional priority) in the system executes floating-point operations. Since no other task executes floating-point operations, a running operation cannot be interrupted by another. Only tasks with the priority 0 execute floating-point operations. If no round-robin scheduling is used, no problems occur since the tasks cannot mutually interrupt. When the round-robin scheduling is used, the task change during floating-point operations is delayed up to the end of the operation (see scheduling rules).

If several tasks assigned to different priorities use floating-point operations, the standard C51 functions "fpsave" and "fprestore" must be used (see C51 documentation). In this case, the present state of an interrupted floating-point operation must be stored with "fpsave" prior to floating-point operations. After the operation, the state must be restored again with "fprestore" (same as using floating-point operations in interrupt functions for C51 programs without RTX-51). If "fpsave" is called, then no RTX function is to be called until the function "fprestore" is executed (i.e. no RTX functions are allowed between "fpsave" and "fprestore").

- The use of floating-point operations is unproblematic only in one task or exclusively in tasks with priority 0 (also with round-robin scheduling).

- In all other cases, the standard C51 functions "fpsave" and "fprestore" must be used. If "fpsave" is called, then no RTX function call is allowed unless "fprestore" is executed.

### **Use of the C51 Runtime Library**

No restrictions apply for all standard library functions which are reentrant (see C51 documentation).

In regard to the small number of functions which are not reentrant, the user must ensure that these are not simultaneously used by several tasks.

### **Register Bank Default**

RTX-51 assigns register bank 0 to all standard tasks. Fast tasks receive register banks 1, 2 or 3 (selectable with the "#pragma REGISTERBANK (x)" directive).

During a task change, RTX-51 automatically selects the currently required register bank.

RTX-51 tasks and functions used by it must not be provided with the usingattribute (RTX-51 generates the register bank switching). The usingattribute is only permissible for C51 interrupt functions.

### **Use of the C51 Special Library**

C51 contains a special library for supporting the arithmetic unit and multiple data pointers of some 8051 derivatives (80C517/537, DALLAS 80C320 and some AMD chips).

The arithmetic unit can be used along with RTX-51. Note, however, that these functions are not interrupt capable. For this reason, only one task or only tasks with the priority 0 may use the arithmetic unit.

Multiple data pointers are not supported by RTX-51. If special library is to be used, the option MOD517(NODP8) must be used. There is only one way to take advantage of multiple data pointers, when running RTX-51: sections using multiple data pointers must be globally protected against interrupts. Solely under this condition the option MOD517 (or MODAMD) is acceptable.

The C51 special library uses multiple data pointers to speed up the functions 'memcpy', 'memmove', 'memcmp', 'strcpy' and 'strcmp'. If locking out of interrupts is not a problem concerning the interrupt response time, then a sequence like shown below is acceptable with RTX-51:

Example for Infineon 80C517(A)/537(A):

```

unsigned int oldbuf[100];

unsigned int newbuf[100];

/* Enable usage of multiple data pointers */

$pragma MOD517

...

/* Disable interrupts globally */

EA = 0;

/* Copy data using multiple data pointers */

memcpy (newbuf, oldbuf, sizeof(newbuf));

/* Re-enable interrupts globally */

EA = 1;

/* Disable usage of multiple data pointers */

$pragma NOMOD517

```

Example for Dallas 80C320 and (some) AMD chips:

```

unsigned int oldbuf[100];

unsigned int newbuf[100];

/* Enable usage of multiple data pointers */

$pragma MODAMD (DP2)

...